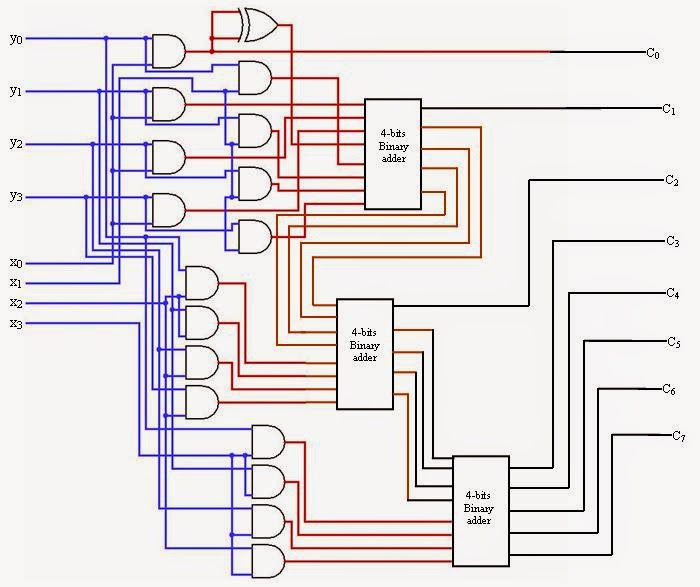

Multiplier adder topologies implementation delay Block diagram of 8-bit multiplier using 4-bit carry pre-computation Bit unsigned multiplier adder

Block diagram of an 8-bit multiplier. | Download Scientific Diagram

4-bit multiplier design2 Multiplier implementation topologies delay Alu bit diagram multiplier block mini introduction figure final

Block diagram of an 8×8 bits pipelined multiplier

4: block diagram of an unsigned 8-bit array multiplier.Block diagram of an 8-bit multiplier. Architecture of 16x16 bit multiplier using 8x8 bit multiplier blockBlock diagram of an 8-bit multiplier..

Multiplier bit 16x16 8x8Functional block diagram for an 8-bit 8-cycle reconngurable multiplier Block diagram of an unsigned 8-bit twin-precision multiplier that is4 bit multiplier circuit diagram.

Multiplier proposed dhande

Multiplier binary bit diagram algorithm collaborative learning figureMultiplier computation Multiplier array unsigned reconfigurable multipliersBlock diagram of an 8-bit multiplier..

Multiplier pipelinedMultiplier design2 The block diagram for the 2-bit multiplierBlock diagram of an 8-bit multiplier..

Block diagram of the (a) proposed 2-bit multiplier and (b) 2-bit

Binary multiplication methodsFunctional block diagram for an 8-bit 8-cycle reconngurable multiplier Block diagram of array multiplier for 4 bit numbersBlock diagram of the multiplier: two 8-bit operands a and b are.

Binary multiplier bit multiplication circuit parallel numbers two backAdder multiplier ripple schematic delay topologies space Multiplier operands multipliedCollaborative learning: binary multiplier.

Block diagram of an 8-bit multiplier.

.

.

Block Diagram of 8-bit Multiplier Using 4-bit Carry Pre-Computation

4: Block diagram of an unsigned 8-bit array multiplier. | Download

Collaborative Learning: Binary Multiplier

Block diagram of an 8-bit multiplier. | Download Scientific Diagram

Block diagram of an 8-bit multiplier. | Download Scientific Diagram

Block diagram of the (a) proposed 2-bit multiplier and (b) 2-bit

Functional Block Diagram for an 8-bit 8-cycle Reconngurable Multiplier

Binary Multiplication Methods - ElectronicsHub